Navigating the Labyrinth of Software Development: Understanding Makefiles

Related Articles: Navigating the Labyrinth of Software Development: Understanding Makefiles

Introduction

With enthusiasm, let’s navigate through the intriguing topic related to Navigating the Labyrinth of Software Development: Understanding Makefiles. Let’s weave interesting information and offer fresh perspectives to the readers.

Table of Content

- 1 Related Articles: Navigating the Labyrinth of Software Development: Understanding Makefiles

- 2 Introduction

- 3 Navigating the Labyrinth of Software Development: Understanding Makefiles

- 3.1 Deciphering the Language of Makefiles

- 3.2 Unveiling the Benefits of Makefiles

- 3.3 Navigating the Make Command: A Deeper Dive

- 3.4 Unveiling the Power of Makefiles: Real-world Applications

- 3.5 Frequently Asked Questions (FAQs)

- 3.6 Tips for Effective Makefile Creation

- 3.7 Conclusion

- 4 Closure

Navigating the Labyrinth of Software Development: Understanding Makefiles

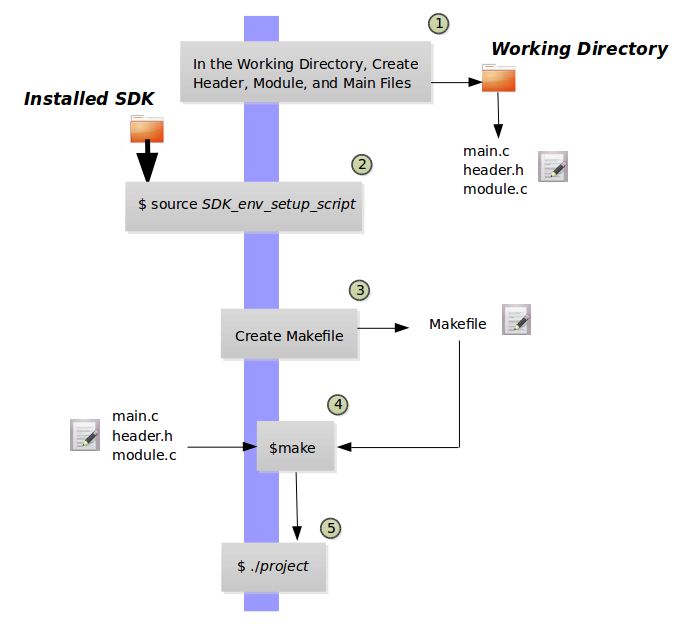

Software development, at its core, is a process of building complex structures from intricate components. These components, often referred to as source files, are transformed into executable programs through a series of steps known as compilation, linking, and execution. Managing this intricate process, particularly when dealing with large projects involving numerous files, can quickly become overwhelming. This is where the power of Makefiles comes into play.

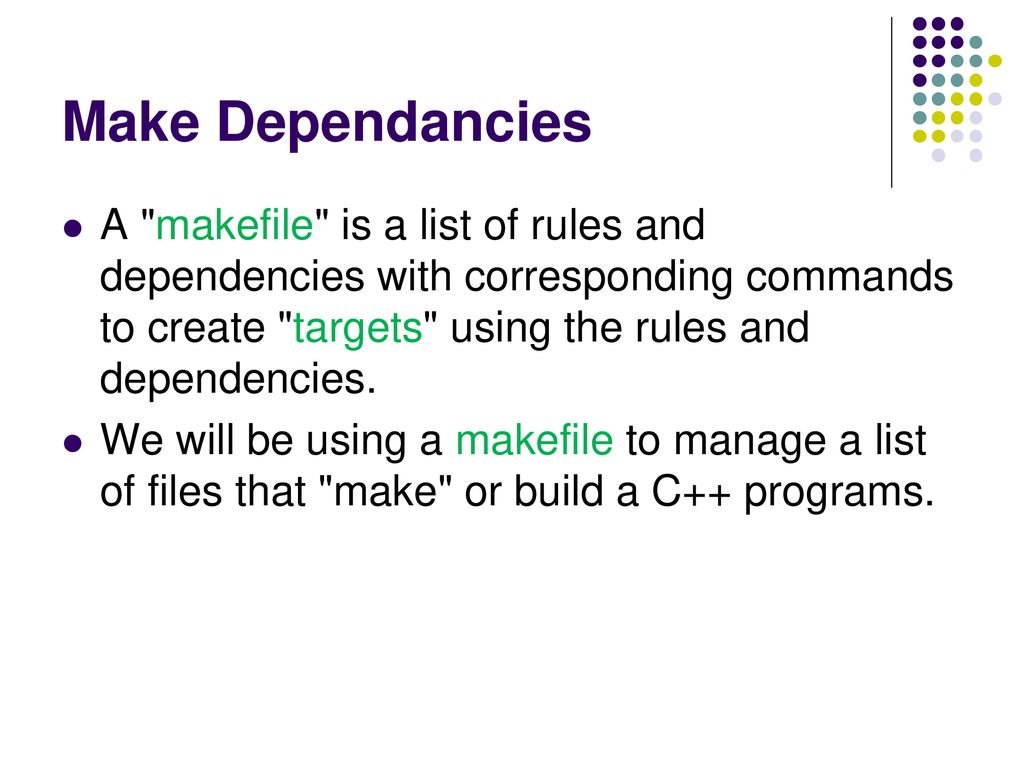

A Makefile, in essence, acts as a blueprint, providing a structured approach to the compilation and linking process. It defines a set of rules and dependencies that guide the build process, ensuring that the final executable program is created efficiently and accurately. This blueprint, written in a simple language, automates the tedious tasks involved in software development, allowing developers to focus on the creative aspects of their work.

Deciphering the Language of Makefiles

A Makefile is composed of a series of rules, each consisting of a target, prerequisites, and a command. The target represents the file or action to be generated, while the prerequisites are the files or actions that must be completed before the target can be created. The command specifies the instructions to be executed to achieve the target.

Example:

# Target: executable file "myprogram"

myprogram: main.o functions.o

gcc main.o functions.o -o myprogram

# Prerequisites: object files "main.o" and "functions.o"

main.o: main.c

gcc -c main.c -o main.o

functions.o: functions.c

gcc -c functions.c -o functions.oIn this example, the target "myprogram" depends on the prerequisites "main.o" and "functions.o". The command "gcc main.o functions.o -o myprogram" links these object files to create the executable "myprogram". Similarly, the object files "main.o" and "functions.o" are created from the source files "main.c" and "functions.c", respectively.

Unveiling the Benefits of Makefiles

The use of Makefiles offers a plethora of benefits for software developers, streamlining the build process and enhancing overall productivity:

- Automation: Makefiles automate the build process, eliminating the need for manual commands and ensuring consistent results.

- Efficiency: By only compiling and linking the necessary files, Makefiles significantly reduce build times, saving valuable developer time and resources.

- Dependency Management: Makefiles manage the dependencies between files, ensuring that changes are propagated correctly and that only the affected files are rebuilt.

- Flexibility: Makefiles are highly customizable, allowing developers to tailor the build process to specific project requirements.

- Maintainability: Makefiles provide a clear and concise representation of the build process, making it easier to understand and maintain the project.

Navigating the Make Command: A Deeper Dive

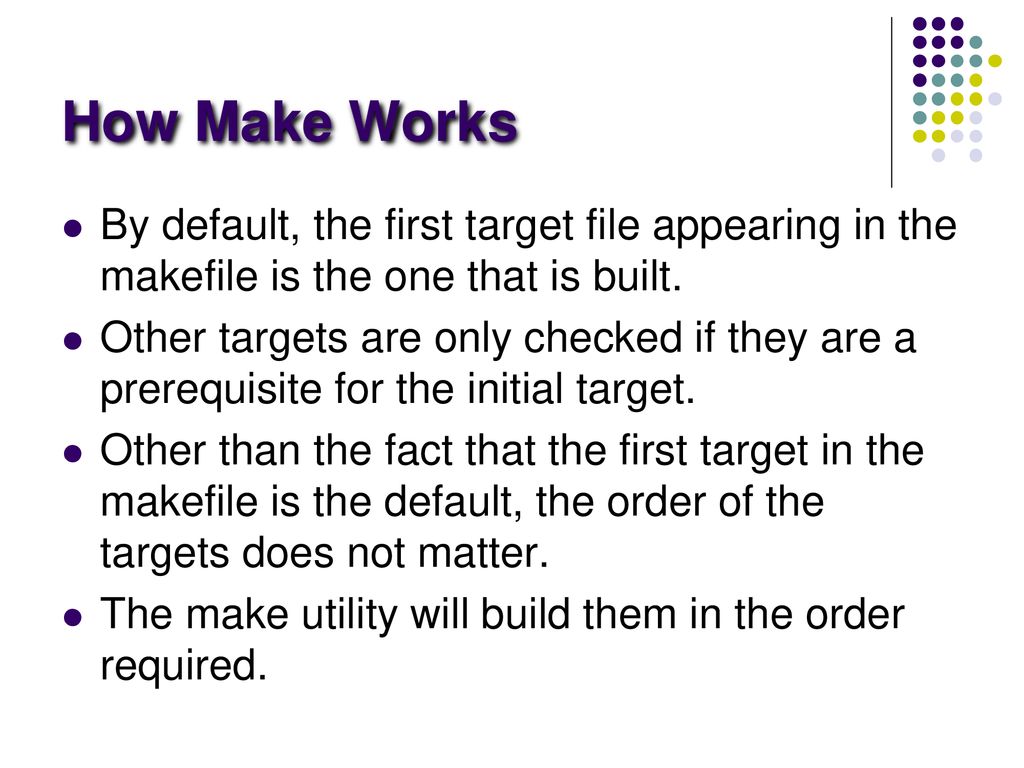

The "make" command, a powerful tool included in most Unix-like operating systems, interprets and executes the instructions defined in the Makefile. By running "make", the developer initiates the build process, triggering the execution of the appropriate commands based on the defined rules.

Common Make Commands:

- make: Builds the default target specified in the Makefile.

- make target: Builds the specified target.

- make clean: Removes intermediate files generated during the build process.

- make all: Builds all targets specified in the Makefile.

Unveiling the Power of Makefiles: Real-world Applications

Makefiles are widely used in various software development environments, particularly in projects with a large number of source files and complex dependencies. Some common applications include:

- C/C++ Development: Makefiles are essential for managing the compilation and linking process in C/C++ projects, particularly when dealing with large codebases and complex dependencies.

- Python Development: While Python projects often rely on tools like "pip" for dependency management, Makefiles can be used for tasks like building custom extensions or managing complex build processes.

- Web Development: Makefiles are used for automating tasks like compiling Sass or Less files, minifying JavaScript code, and deploying websites.

Frequently Asked Questions (FAQs)

Q: What is the purpose of a Makefile?

A: A Makefile automates the build process, ensuring that the correct steps are taken to compile, link, and execute a software program. It defines the dependencies between files and the commands needed to create the final executable.

Q: How do I create a Makefile?

A: A Makefile is a text file written in a simple language that defines the build process. It consists of rules, each defining a target, prerequisites, and commands. You can create a Makefile using any text editor and save it with the name "Makefile".

Q: What are the advantages of using Makefiles?

A: Makefiles offer several advantages, including automation, efficiency, dependency management, flexibility, and maintainability.

Q: Are Makefiles only used in specific programming languages?

A: Makefiles are not language-specific and can be used in various programming languages, including C, C++, Python, Java, and others.

Q: How do I use Makefiles with different programming languages?

A: The specific commands and rules used in a Makefile may vary depending on the programming language and build system. For example, the commands used to compile a C program will differ from those used to compile a Python program.

Q: Can I use Makefiles for other tasks besides building software?

A: Yes, Makefiles can be used for a variety of tasks, such as automating scripts, generating documentation, or running tests.

Tips for Effective Makefile Creation

- Start Simple: Begin with a basic Makefile and gradually add more rules and dependencies as your project grows.

- Use Descriptive Names: Choose descriptive names for targets and variables to make the Makefile easier to understand.

- Comment Your Code: Add comments to explain the purpose of different rules and commands.

- Use Variables: Define variables to store common values and make the Makefile more concise.

- Use Macros: Define macros to encapsulate frequently used commands and make the Makefile more efficient.

- Test Your Makefile: Regularly test your Makefile to ensure that it is working correctly.

Conclusion

Makefiles are a powerful tool for software developers, streamlining the build process and enhancing overall productivity. By automating tasks, managing dependencies, and providing a clear structure for the build process, Makefiles enable developers to focus on the core aspects of their work, leading to more efficient and robust software development. Understanding and utilizing Makefiles can significantly improve your development workflow, ultimately leading to better software and a more enjoyable development experience.

Closure

Thus, we hope this article has provided valuable insights into Navigating the Labyrinth of Software Development: Understanding Makefiles. We thank you for taking the time to read this article. See you in our next article!